Ternary Test Board v2

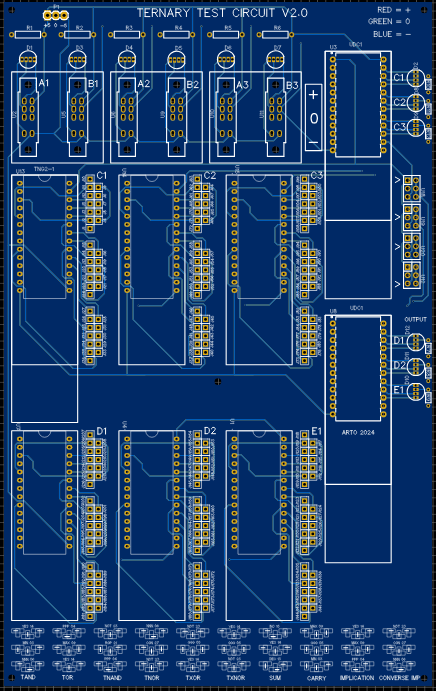

This board design concentrates on the 2 input Ternary Combinations.

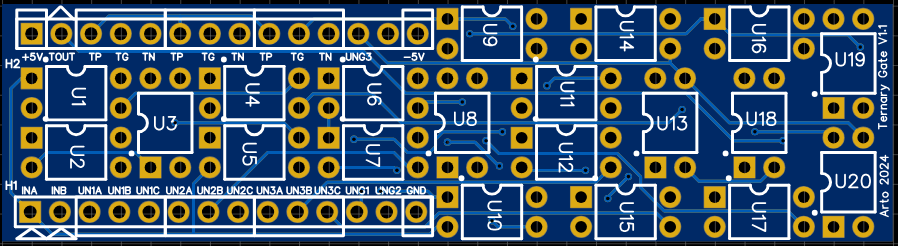

I had made many Ternary Gates, here are 2 preferred designs using optical relays, using a 28 pin form.

The display units are less demanding and can be designed in many ways, here are 3 designs, using 24 pins.

The V9 Ternary display unit requires 100 ohm resistors before grounding, if you use V7 or V8 you can just use shorting wires if you requires them, or just leave in the 100 ohm resistors. ( untested)

First of all the 6 switched inputs relates to three 2 input gates which are arranged to give you a maximum of choice.

The first 2 inputs A1 + B1 are directly combined in C1 to create the 2 output gate, designed by the links you combine in 12 pin matrix on the right side of each TNG2-1 chip.

To make your life easier I have put a number of gates that you can use on the bottom of the main board.

The LED outputs are in three groups:

1] switched inputs (6) A1 B1 A2 B2 A3 B3

2] output from each ternary gate (3) C1 C2 C3

3] output from combinations of 3 ternary gates D1 D2

4] output from the last 2 gates E1

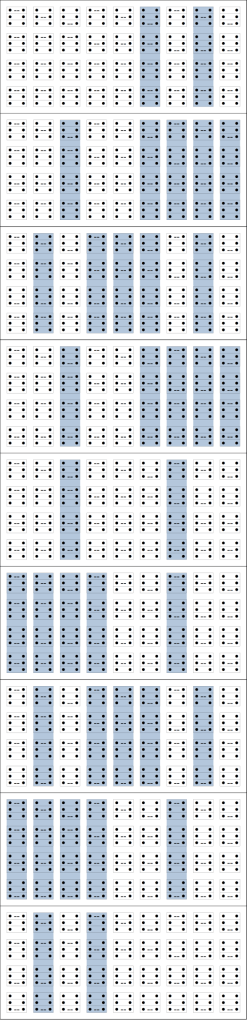

To understand the Ternary Gate link matrix, here is a legend:

_________________ _________________

| | | | _____ | | | |

| + | X | - | | | | + | X | - |

|____|_____|____| | 0 | |_____|_____|_____|

| | ____|_____|_____ | |

| 0 | | | | | | 0 |

|_____| | + | X | - | |_____|

|____|_____|_____| Where X is the input link to the TNG2-1 chip.

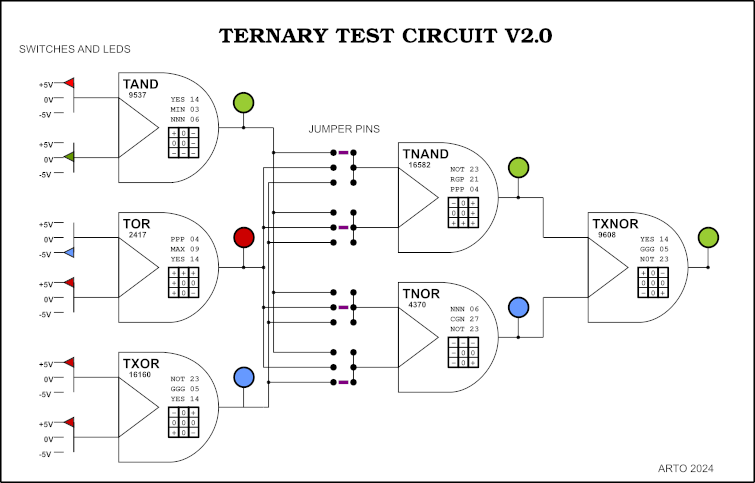

Here is a simple schematic of the test board, set up with various gates and a set of links. I have indicated the outputs from each stage.

Here are the outputs from different input combinations, The first is the same as the diagram:

SW C D E

TAND TNAND TXNOR

1 0 0 0

0

TOR TNOR

-1 1 -1

1

TXOR

1 -1

1

SW C D E

1 1 -1 1

1

-1 1 -1

1

0 0

1

SW C D E

1 1 -1 1

1

1 1 -1

1

1 -1

1

SW C D E

0 0 0 0

0

0 0 0

0

0 0

0

SW C D E

-1 -1 1 1

-1

-1 -1 1

-1

-1 -1

-1

SW C D E

1 0 -1 1

0

-1 1 -1

1

0 0

-1

The jumper settings allows 81 variations, in 3 blocks -1 to 27, 28 to 54, 55 to 81;

I set the basic set up as number 67 from the list above. There are only 36 link combinations that include all three outputs from gates C (they form a top/bottom symmetrical list). Here are the sets:

6 8

12 15 16 17 18

20 22 23 24 26

30 33 34 35 36

39 43

46 47 48 49 52

56 58 59 60 62

64 65 66 67 70

74 76

I hope you can find the many great discoveries of computation inside the Ternary domain, regards Arto.

Ternary Test Boards PCB1E Zipfile

All the PCB and Schematics for this project. EasyEDA files only.

$15.00

Tags: circuit, EasyEDA, logic-gates, rgb led, tand, ternary, trinary, Unary

Leave a comment